摘要:当总线空闲且两个高电平协议的起始位都为高电平时,下降沿的协议结束位为高电平时,出现上升沿。主设备产生所有时钟脉冲,包括确认位的第九个时钟脉冲。当在第一个时钟脉冲期间保持高电平时,这被定义为未确认信号。

一、I2C总线简介I2C总线是飞利浦公司开发的一种简单的双向双线同步串行总线。它只需要两根导线就可以在连接到总线的设备之间传输信息。

主器件用于启动总线传输数据,并产生时钟以打开被传输器件。此时,任何被寻址的设备都被视为从设备。总线上的主从、发送和接收的关系不是恒定的,而是取决于此时的数据传输方向。如果主机要向从设备发送数据,主机首先寻址从设备,然后主动向从设备发送数据,最后主机终止数据传输;如果主机想要从从设备接收数据,主机首先寻址从设备,然后主机接收从设备发送的数据,最后主机终止接收过程。在这种情况下,主机负责产生定时时钟和终止数据传输。

I2C总线是公认的世界标准,50多家公司生产1000多种在不同地方实现的集成电路。此外,通用i2c总线用于各种控制架构,如系统管理总线(SMBus)、电源管理总线(PMBus)、智能平台管理接口(IPMI)、显示数据通道(DDC)和高级电信计算架构(ATCA)。

I2C公交的原理和细节参考本文,感谢作者的安排,受益匪浅。

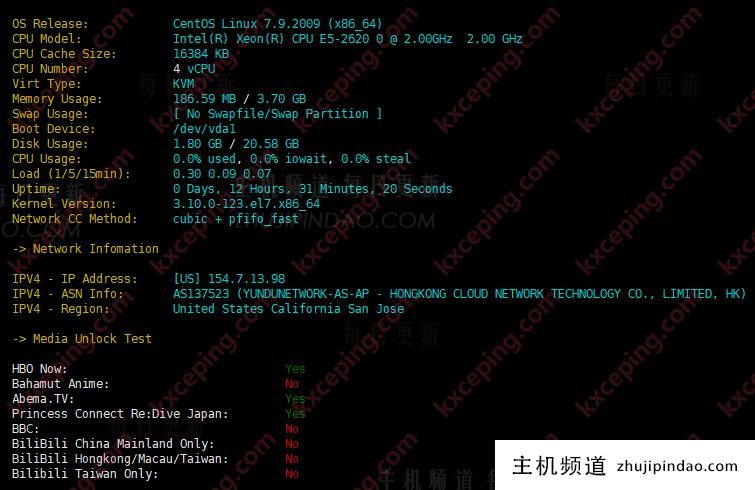

二。I2C总线协议串行数据线(SDA)和串行时钟线(SCL) SDA和SCL是双向线路,通过电流源或上拉电阻连接到正电源电压。连接到总线的器件的输出级必须具有开漏或开集电极,以执行线路和功能。I2C -总线上的数据传输速率在标准模式下最高可达100kbit /s,在快速模式下最高可达400kbit /s,在快速模式下最高可达1 Mbit/s,在高速模式下最高可达3.4 Mbit/s。总线电容限制了连接到总线的接口数量。

数据有效性SDA线上的数据必须在SCL时钟线的高时钟电平期间保持稳定,在低时钟电平期间发生变化(见下图)。所以我们在设计信号的时候,最好的情况是,SDA数据线上的数据在时钟线SCL处于低电平中间时发生变化,SDA数据线上的数据是在时钟处于高电平中间时得到的。

起始和停止位所有数据传输都以START (S)开始,以STOP (P)结束(见下图)。I2C公交闲置:SDA和SCL都高;I2C协议的起始位:SCL高时,SDA有下降沿;I2C协议终止位:当SCL为高电平时,SDA的上升沿出现。起始和停止条件总是由主器件产生。在启动条件之后,总线被认为是繁忙的。在停止条件之后,总线再次空闲一段时间。如果产生重复启动(Sr)条件而不是停止条件,总线将保持忙碌。在这方面,启动(S)和重复启动(Sr)条件在功能上是相同的。

传输1字节格式SDA数据线上传输的每个字节必须为8位长。每次传输可以传输的字节数没有限制。每个字节后必须跟随一个应答位(ACK)。数据从字节的最高有效位(MSB)传输(见下图)。如果从机在执行其它功能(如服务内部中断)之前无法接收或发送另一个完整字节的数据,它可以保持时钟线scl为低电平,并强制主机进入等待状态。当从机准备另一个字节的数据时,它继续发送数据并释放时钟线SCL。

ACK和NACK响应出现在每个字节之后。应答位做出响应,表示该字节已成功接收,可以发送另一个字节。主设备产生所有时钟脉冲,包括确认位的第九个时钟脉冲。应答信号定义如下:在响应时钟脉冲期间,发送方释放SDA线,接收方可以将SDA线拉低,在时钟高电平期间保持低电平。当SDA在第9个时钟脉冲期间保持高电平时,这被定义为不应答信号。然后,主设备可以生成停止条件以终止传输,或者生成重复开始条件以开始新的传输。NACK的产生有五个条件:

-总线上没有带有发送地址的接收器,因此没有设备可以应答。-接收器不能接收或发送,因为它正在执行一些实时功能,并且没有准备好开始与主控制器通信。-在传输过程中,接收器获得它不理解的数据或命令。-传输期间,接收器无法接收更多数据字节。-主接收器必须向从发射器发送传输结束信号。

从设备的设备地址和读写位从设备的地址是I2C协议在传输数据时寻址总线上设备的基础。数据传输遵循下图所示的格式。启动条件后,发送一个从机地址。该地址为7位长,后跟一个数据方向位(R/W)-“0”表示传输(写),而“1”表示请求数据(读)(见下图2)。数据传输总是以主机产生的停止条件结束。然而,如果主机仍想在总线上通信,它可以产生重复的起始条件(Sr)和地址,而不产生停止条件。

从机地址通常由固定位和可变位组成。所谓固定位是指设备被确定为不可改变,不可控制,而可变位通常是设备的硬件,可以通过用户的硬件来连接。例如,在下图的7位设备地址中,前四位1010在工厂是固定的,后三位是用户可以更改的设备硬件引脚。

对于不同的设备,I2C传输格式略有不同。对于存储设备,它也有内存的地址号。在主机发送器件地址且从机存储器做出响应后,主机发送8或16位存储器地址数据来选择存储器地址。等待从机响应后,主机向存储器地址发送数据或从中读取数据。

第三,I2C接口有严格的读写时序,包括写数据时序、读数据时序、连续写数据时序和连续读时序。本实验只实现了写数据时序和读数据时序。I2C数据传输具有高优先级。

图一。写数据时序

图二。读取数据时序根据I2C的读写时序图,我们可以发现读写时序传输顺序为:

首先,当SCL为高电平时,主器件拉低SDA以产生起始信号。主机发送从机地址位(R/W位为0,写)。在下一个时钟周期,主机释放对SDA总线的控制,从机拉低SDA以产生应答位(ACK)。主器件发送要写入或读取的寄存器地址位,在下一个时钟周期,主器件释放对SDA总线的控制,从器件拉低SDA产生应答位(ACK);主设备发送要写入的数据。在下一个时钟周期,主机释放对SDA总线的控制,从机拉低SDA以产生应答位(ACK)。主设备再次产生开始信号(这一点非常重要!),然后再次发送从设备地址位(R/W位为1,读),主设备释放SDA总线控制,从设备产生应答位,然后从设备发送数据,主设备不产生应答位;最后,在SCL高电平期间,主机将SDA拉高以产生结束信号。因此,您可以相应地绘制一个状态机图:

图3。事不宜迟,状态机的代码如下:

模块IIC模块(输入clk,//50mhz时钟频率输入复位,输入start,// start信号,注意!!!启动信号的高电平持续时间最好约为一个scl高/低电平周期,并且不应太长。输入WR_OR_RE,//读/写控制,0=写,1=读输入[6:0]device addr,//从器件地址,7bitinput [7:0] RegisterAddr,//寄存器地址输入[7:0] WriteData,//要写入的数据,outputregscl,inoutsda,outputregdone,outputreg [7: 0] readdata//从从器件读取的8位数据);参数CLK_FREQ = 50_000_000,SCL _ FREQ = 100 _ 000;//SCL的频率设置为100 khz local param SCL _ CNT = clk _ freq/(2 * SCL _ freq);//为了让signalTap能够观察到足够长时间的窗口时间,我提高了频率。其实不需要除以2//状态机状态标志,比如参数Idle = 4“D0,Start = 4“D1,WR _ ADDR = 4”D2,WR _寄存器= 4“D3,WR _数据= 4“D4和Re _ Start = 4”。reg [7:0] state =空闲,next_state =空闲;//设备地址//参数deviecaddr = 7 " b0011101reg[7:0]DeviecAddr _ wr;reg[7:0]DeviecAddr _ re;always @(*)beginDeviecAddr _ wr = { DeviecAddr,1 " B0 };DeviecAddr_re = {DeviecAddr,1 " B1 };End//SCL&SCL _ CNT ---50mhz时钟产生100kHzscl时钟reg[7:0]SCL _ CNT;如果(复位)开始scl,则始终@(posedge CLK)开始

主机频道

主机频道

评论前必须登录!

注册