摘要:将模拟设计下载到硬件实验框以进行验证。 实验引脚将销钉锁定到八个键的相应销钉。

1。实验目的

(1)学习并掌握Quartus II(2)学习简单的计时电路设计和硬件测试。 (3)学习使用VHDL语言方法进行逻辑设计输入(4)学会设计流坡道电路,并熟悉实验开发系统中执行输入和模拟步骤的原理

2。实验设备和设备

(1)一台PC。 (2)一组Quartus II开发软件(3)一组EDA实验开发系统(EP1C12Q240C8)

3。实验原理

FPGA上的所有I/O控制块都可以用每个1/O PIN作为输入端口进行配置,但是该配置会由系统自动完成。当输入端口配置为使用输入端口时,I/O控制模块将三个状态缓冲区的控制终端直接接地,从而允许I/O引脚用作专用输入引脚。 key1 -如果键输入发生在键8中,则正确分配和锁定了引脚,并且一旦检测到键盘输入,请继续确定键盘值并继续进行相应的过程。

4。实验内容

(1)可以使用基于VHDL语言设计的简单逻辑电路来控制LED流灯。该电路包括三个输入和八个输出。 输入信号是清除信号端子CLR,时钟信号CLK和有效信号ENA,输出信号Y连接到八个光学表达二极管。 如果清除信号端子的CLR较低,则清除系统并关闭所有八个LED灯。 当ENA输入信号高并且CLK的上升边缘到达时,流量开始流动,并且流量从D1到D2到D3,到D4,到D5到D5至D6至D7至D7至D8,返回到D1。 如果ENA输入信号较低,则荧光岩将暂停并保持其原始状态。 相应的关系如下表所示

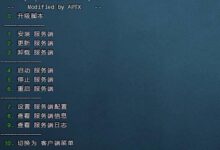

(2)为Quartus II V HDL文本设计流动坡道电路。编辑,编译,集成,调整和模拟设计。 要进行验证,请将模拟设计下载到硬件实验框中。 注意:3个输入信号线(ENA连接到键1,CLR连接到键2,CLK连接到CLK0)和8个输出线(连接到光学光线发射二极管指示灯)。为了在硬件测试期间易于观察,流速在4Hz左右是最佳的。在测试过程中,由于输入信号的变化而观察到输出信号的变化。 图中显示了流动坡道控制电路的模拟。

实验性PINLOCK:8键:键1-8对应于PIN 233、234、235、236、237、238、239、240,分别在FPGA上。 八个光学发射二极管:发光。 DIODES D1至D8分别对应于FPGA的168至161。 时钟端口:CLKO支持28 CLK2,CLK5支持152,CLK5支持152,CLK5支持152,而Clk90支持29。

V.实验程序

(1)启动Quartus II创建一个空白项目,然后命名hight8.qpf。 (2)创建一个新的VHDL源程序文件hight8.vhd,输入并保存程序代码以运行全面的编译。如果在编译过程中发现错误,请查找并修复它,直到汇编成功。 (3)选择目标设备并锁定相应的引脚。此处选择的设备是Altera旋风系列中的EPIC12Q240C8芯片。 将未使用的引脚设置为三态输入。 接下来,找到错误并修复它。 (4)在整个过程中编译项目文件,如果在编译过程中发现错误,直到汇编成功为止。 连接到PC打印机,(5)卸下Altera Byte Blaster II下载电缆,然后将电缆的两端连接到PC打印机的并行端口和实验框的JTAG下载端口。打开电源,运行下载命令,将程序下载到FPGA设备上,然后在发光二极管LED的ON/OFF状态下在LED1的LED8上观察它。

6。实验扩展

根据以前的实验,已经实现了其他模式,控制了八个LED灯以显示模式显示,并设计了三种模式。示例代码:

图书馆ieee; - -扩展灯顶文件ieee.std_logic_1164.all;实体Hight8是- -顶级实体名称端口(- -定义端口数据CLK:STD_LOGIC; - - - -终端输入端口ENA:STD_LOGIC; - - - - -定义了可启用的信号输入port lad lad lad led:out std_logic_vector k4 k4 k4 k4 k4(7) LED灯输出端口C:STD_LOGIC_VECTOR(7向0);

主机频道

主机频道

评论前必须登录!

注册